Министерство науки и высшего образования Российской Федерации Сибирский федеральный университет

## METHODS OF DESIGN AUTOMATION OF HETEROGENEOUS COMPUTING SYSTEMS AND INFORMATION MODELS OF OBJECTS

Монография

Электронное издание

Красноярск СФУ 2020 УДК 004.41'22 ББК 32.97-02 Б820

Борде Бернгард Исаакович

Б820 Methods of design automation of heterogeneous computing systems and information models of objects: Монография / Б. И. Борде. – Электрон. дан. (2,4 Мб). – Красноярск: Сиб. федер. ун-т, 2020. – Систем. требования: РС не ниже класса Pentium I; 128 Мb RAM; Windows 98/XP/7; Adobe Reader V8.0 и выше. – Загл. с экрана.

ISBN 978-5-7638-4367-5

Creating information models of objects is characterized by increased laboriousness, and multivariate design of objects to select the optimal solution according to the efficiency criterion increases the time of creating objects. Technological progress and competition are forcing to reduce the time for designing and creating new facilities. The creation of a research software package that complements the design system can reduce the total time and eliminate human error. From the conceptual description of the project in the form of a formalized task (FT), a project in CAD or a batch file for automatic execution can be automatically obtained. The execution time of the command file is reduced by an order of magnitude compared to the command set in CAD. The possibility of error is excluded in the usual and proposed design option. A technology has been created that generalizes design at different levels of abstraction.

УДК 004.41'22 ББК 32.97-02

ISBN 978-5-7638-4367-5

© Сибирский федеральный университет, 2020

Электронное научное издание

Подготовлено к публикации издательством Библиотечно-издательского комплекса

Подписано в свет 30.10.2020. Заказ №11409 Тиражируется на машиночитаемых носителях

Библиотечно-издательский комплекс Сибирского федерального университета 660041, г. Красноярск, пр. Свободный, 82a Тел. (391)206-26-16; http://rio.sfu-kras.ru E-mail: publishing house@sfu-kras.ru

### **CONTENTS**

| Introduction                                                               | 5    |

|----------------------------------------------------------------------------|------|

| 1. Development of computer systems and means for their modeling and        |      |

| design                                                                     | . 10 |

| 1.1. The development of heterogeneous computing systems                    | . 10 |

| 1.2. Abstraction levels of computing systems                               |      |

| 1.3. The development of heterogeneous computing systems                    |      |

| 1.4. Complexes for modeling and designing heterogeneous computing          |      |

| systems                                                                    | . 17 |

| 2. Principles of construction of multi-level systems of design of          |      |

| heterogeneous computing systems                                            | . 20 |

| 2.1. Description of design solutions for computing systems                 | . 20 |

| 2.2. Structural synthesis of computing devices and systems                 |      |

| 2.3. Analog-to-digital devices of computing systems                        | . 28 |

| 2.4. Inhomogeneous computing systems based on microEBM                     | . 32 |

| 2.5. Computing systems from network devices and computers                  | . 43 |

| 2.6. The processes of synthesis and analysis of heterogeneous computing    |      |

| systems                                                                    | . 44 |

| 2.7. Principles of building multi-level systems for modeling and designing |      |

| computing systems                                                          | . 46 |

| 2.8. Informational basis for converting descriptions into multi-level CAD  | . 48 |

| 2.9. Formalized task and algorithms for automated analysis                 | . 53 |

| 3. Multifunctional models of components                                    | . 60 |

| 3.1. Component Abstraction Levels                                          | . 60 |

| 3.2. Component Models                                                      |      |

| 3.3. Representation of models in CAD "COD"                                 |      |

| 3.4. Models of components for providing CAD interfaces "COD" with PCA      | 4D   |

| ~ <i>j</i> ~ · · · === · · · · · · · · · · · · · ·                         | . 70 |

| 3.5. Automation of the formation of models of components for CAD PCAI      | )77  |

| 3.6. Automation of the formation of models for text descriptions of        |      |

| information support for the life cycle of computing systems                | . 84 |

| 3.7. Models of components for providing CAD interface "COD" with           |      |

| integrated CAD software CATIA v5                                           |      |

| 3.8. Models of components for providing CAD interface "COD" with virtu     | al   |

| reality environment                                                        | . 92 |

| 3.9. Synthesis of a model and operation algorithms of an analog-to-digital |      |

| subsystem with a USB interface                                             | . 94 |

| 4. Implementation of a multilevel system of modeling and design of         |      |

| heterogeneous computing systems                                            | 101  |

| 4.1. The structure and functions of the software package                   |      |

| 4.2. Information support of modeling and design of computing devices and   |      |

| systems                                                                    | 111  |

| 4.3. Formalized task for automated analysis                                |      |

| 4.4. CAD parameters and data structures                                    | 116  |

| 4.5. Interfaces of research CAD COD with PCAD design automation         |       |

|-------------------------------------------------------------------------|-------|

| system                                                                  | 123   |

| 4.6. Research CAD Interfaces with PCAD200x Systems                      | 130   |

| 4.7. The results of formalized tasks                                    |       |

| 5. Automation of the design of information models of objects and comp   | uter  |

| systems                                                                 |       |

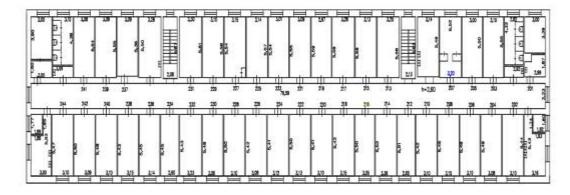

| 5.1. Information models of objects in CAD                               |       |

| 5.2. Designing information models of objects at various levels of the   |       |

| hierarchy                                                               | 147   |

| 5.3. Remote execution of formalized tasks in the INFRAWORKS             |       |

| environme                                                               | 150   |

| 5.4. Campus Design at INFRAWORKS                                        |       |

| 6. Local execution and network services for modeling and designing      |       |

| heterogeneous computing systems                                         | 156   |

| 6.1. Software and hardware complexes CAD                                |       |

| 6.2. Local execution of a formalized task on personal computers in Wind | lows, |

| Linux, and OS/2                                                         | 158   |

| 6.3. Network services and formalized tasks in the Internet environment  | 167   |

| Conclusion                                                              | 173   |

| Bibliography                                                            | 175   |

| Supplement 1. Brief Glossary                                            |       |

| Supplement 2. Acts of use of work                                       |       |

| Supplement 3. Basic events in computer science and SibFU                |       |

#### INTRODUCTION

Development computer technology is accompanied by an increase in the complexity and variety of machines [1, 4, 6, 91] with a decrease in switching energy and the cost of computing operations. The implementation of these requirements is possible only in conditions of complex automation of production of computer equipment and components. The complexity of the components is constantly increasing, therefore, the automation of the design of computer equipment and components is an urgent task. Various computer-aided design systems (CAD) are known: industrial, educational, research and experimental advanced systems for checking the principles of action.

In a short period of 60 years (1956-2016), the path has gone from the first transistors of NPO Svetlana for a prototype of computers and desktop analog machines MN-7 on lamps to mobile devices and large data centers of Sberbank in Skolkovo [I6, I8, I24], designed in CAD REVIT [I1]. In all machines with an index, the MH model is nonlinear; diodes on a typesetting field for continuous logic operations and in nonlinearity blocks were used [140, 141].

Industrial CAD systems belong to the well formalized technical stages of design and are divided into specialized and integrated. Integrated CAD systems are distinguished by an expanded set of components and a variety of connectors and ports with different operating principles. The first specialized CAD of computers was CAD CASPI [9], created at ITMiVT RAS under the supervision of acad. S. A. Lebedev. As the specialized industrial CAD systems for computing systems, the domestic system Prim5.3, GRIF4 [78] and foreign CAD systems for personal computers are used: PCAD, ALTIUM, ORCAD, CADDY, PADS, EAGLE, CADSTAR. As integrated industrial CAD systems for stationary objects, we consider CAD systems from Autodesk Revit and Infra Works, ASCON Renga, working with the BIM object information model, in accordance with GOST and international standards ISO [I28-I30]. As integrated industrial CAD systems for mobile objects, we consider CATIA CAD systems.

Important is the adoption of professional standards for the training of specialists in the creation and modification of integration solutions, code 06.041 of the Ministry of Labor of the Russian Federation in 2017 [I31]. The purpose of the preparation is the integration of information systems and cloud services. Work should be carried out using automated systems. Professional standards must be consistent with industry needs for specialists.

Educational research CAD (UI CAD) correspond to the early poorly formalized design stages. In the early stages of design, synthesis and analysis of many variants of computing devices and systems is desirable. The goal of creating the COD (Conceptual Object Design) software and methodological complex is to increase the level of complexity of the tasks of designing heterogeneous computing devices and systems [12-15] and to improve the engineer's labor productivity.

For descriptions of designed objects in a low-level language used in industrial CAD, the scope of description is proportional to the number of options.

The description of objects in a high-level language allows us to approximate the volume of the description of many objects of one class to the volume of the description of one object. In order to reduce the volume of descriptions, multilevel models of computing systems are used.

The levels of models of computing systems correspond to various tools, the complex of which is implemented in computer-aided design systems. Distinguish CAD of high and low levels. Low-level CAD systems correspond to the lower levels of model abstraction and are used for functional-logical and design. High-level CAD systems provide a description of many technical solutions for system and structural-algorithmic design.

The design process of complex systems and computers in particular is an iterative process of downward and partially upward design at the lower levels. High-level CAD systems are effective for automating the conversion of design decisions during the transition to various low-level CAD systems. The complex of tools for automating the conversion of design decisions between CAD systems of various levels is called the interface in the work.

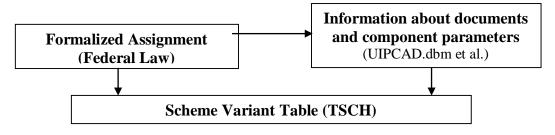

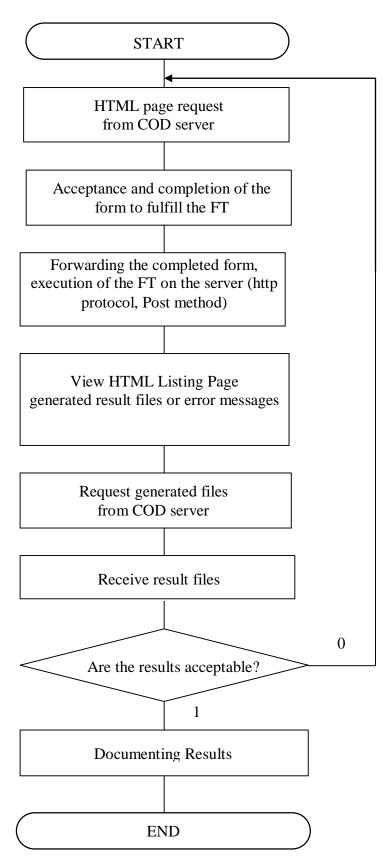

A design decision perceived by a formal system is called a formalized task, which consists of various sections of a description of design decisions. A single entry of formalized tasks is desirable regardless of the number of applications. The conversion of a single formalized task into the format of various CAD systems is provided by the interface between high-level CAD and a specific low-level CAD. The standards for the description of electronic equipment EDIF (Electronic Data Interchange Format) and STEP (Standard for Exchange of Product data) ISO 10303 only partially provide conversion, as they are used only for the external representation of formalized tasks.

The monograph complements the textbooks [101-103, 110], and it considers a multi-level model of a computer system, and features of synthesis and analysis. The main attention is paid to the automated analysis of heterogeneous computing systems with digital and analog signals at various levels of abstraction with a procedure-oriented component-wise description of many technical solutions based on standard universal high-level programming languages and non-procedural descriptions of design solutions at the lower levels.

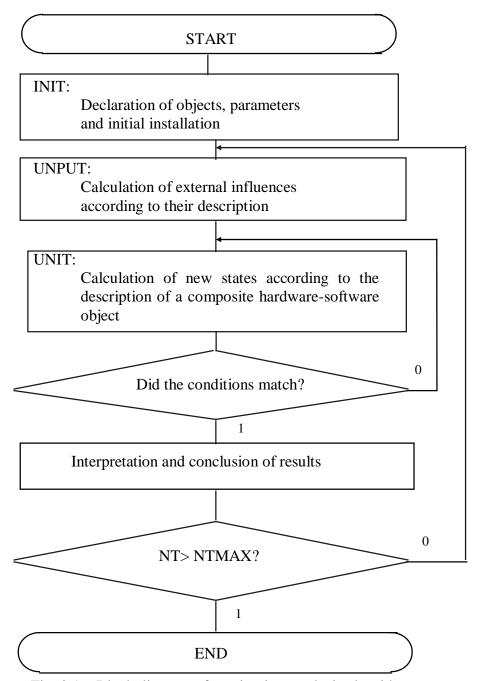

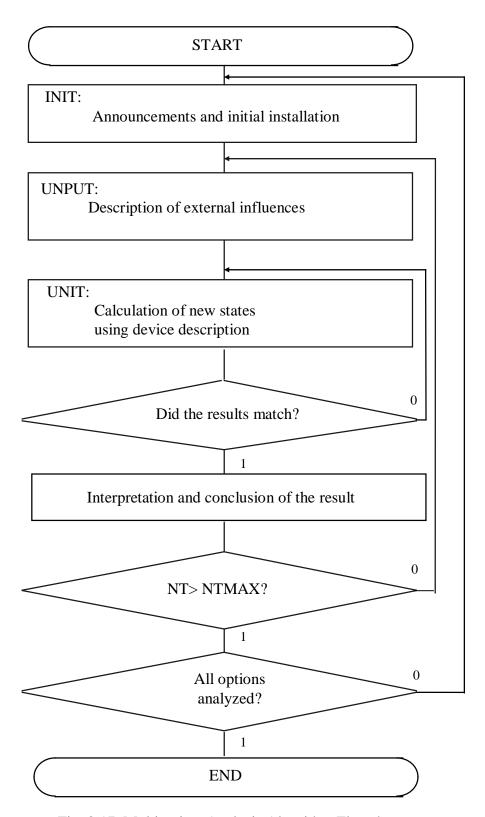

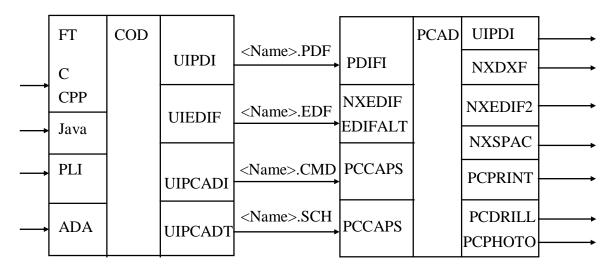

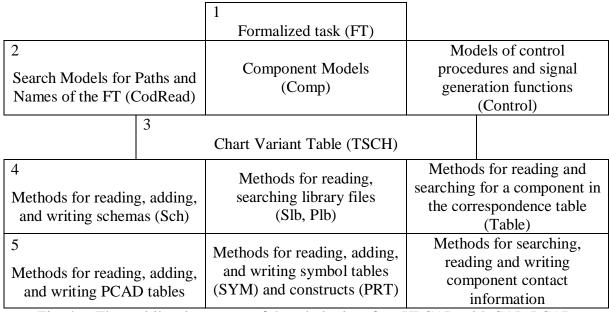

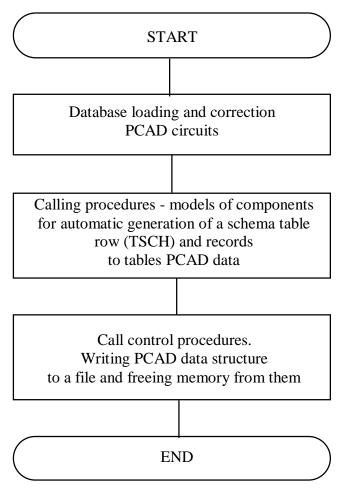

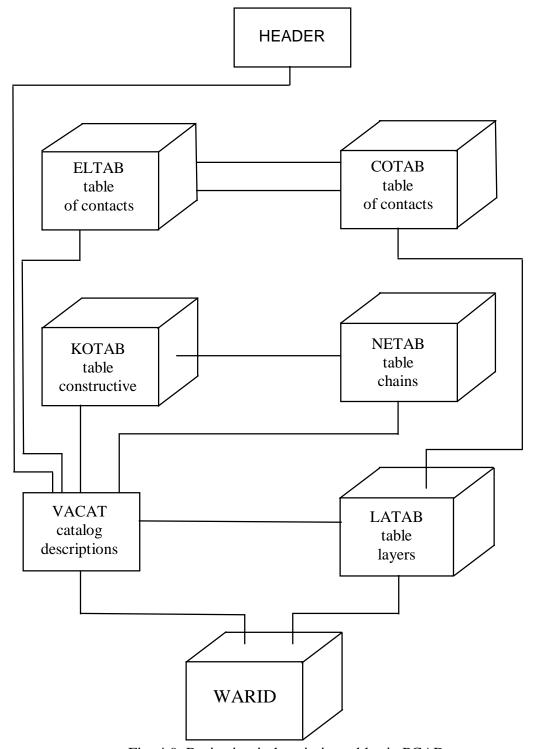

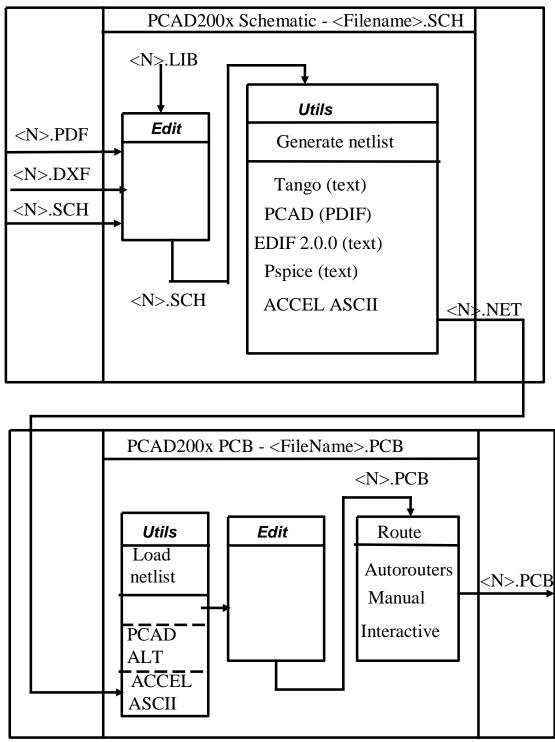

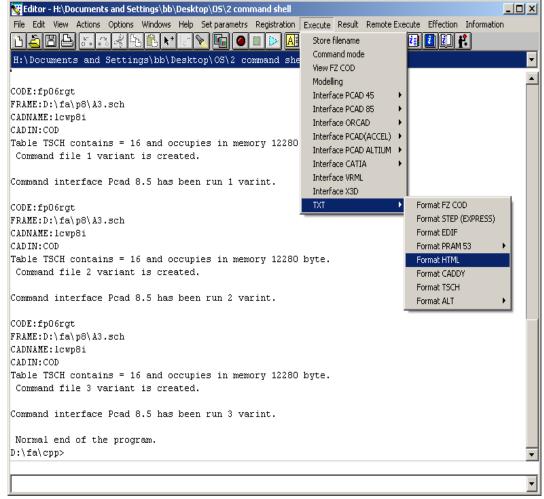

For computer-aided design, starting from the early stages, under the guidance of the author, a high-level CAD and research CAD system was developed to automate the analysis of the operation of computing devices and systems and automatically convert formalized tasks to a low-level CAD format. A distinctive feature of UI CAD is the multiple use of a single formalized task for various applications and multifunctional component models with a common interface. The main application is an automated analysis of the operation of a device or system described in a formalized task. The formalized task describes the structure of the device or system and external influences. The main results of the analysis are timing charts and resource estimates, and with additional applications, the conversion of a formalized task into the format of one of the industrial CAD systems or a virtual reality language. Automation of the conversion of a formalized task to the format of a specific CAD is called an

interface with this CAD. The use of a single formalized task for various applications is provided by multifunctional component models with a common interface. An interface is defined by syntax and semantics tables for each type of component. Models of all types of components for each application are combined into static or dynamic libraries. A dialog box ensures that the application and component model libraries match. Automation of analysis and assessment of resources allows an engineer or student to focus on creative design procedures for the synthesis of descriptions, and automatic resource assessment makes it easier to choose the best solution. CAD has an interface with industrial CAD systems for importing and exporting descriptions.

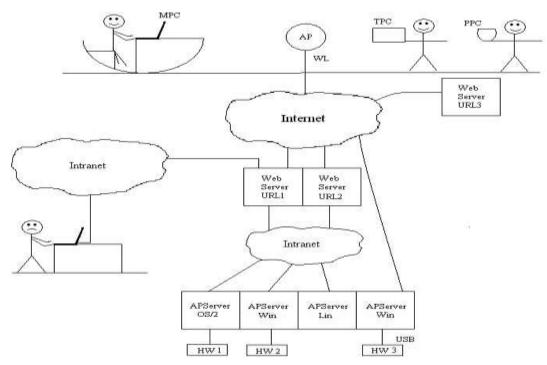

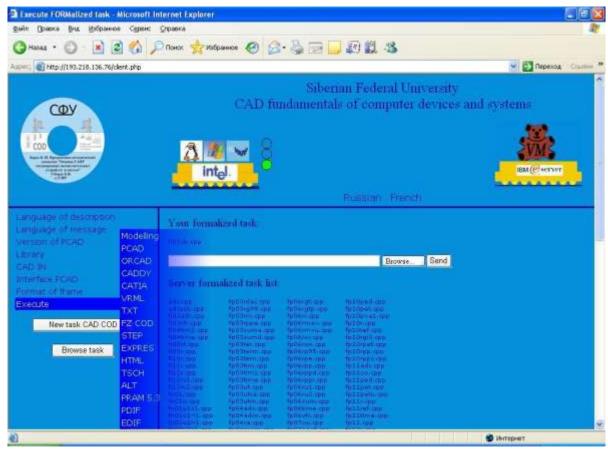

The software is implemented for personal computers and servers, which allows you to use the software and methodological complex for local and distance learning. On personal computers, the complex is implemented in Windows, LINUX, and OS / 2 environments. The server part of the complex is implemented in Windows, LINUX, OS / 2 environments, in the dialog processing subsystem (PDO or PTS) of the S390 virtual machine system (VM / ESA, zVM). Formalized tasks can be performed on a personal computer or transferred for execution to application servers via the Internet. Currently, all servers are located on virtual machines of the data center of the Siberian Federal University and form the basis of the system of distance educational technologies (DOT) of the Siberian Federal University. Network services for training are hosted on e.sfu-kras.ru, and formalized project tasks are performed on the CAD UI on application servers. Many sample projects are hosted on application servers. Application servers can interface with real hardware. Application servers and methodical server are located on the virtual machines of the SibFU data center and are accessible on the Internet. This provides an environment for interactive online learning. Results are sent to users by e-mail or accepted by the user. In cloud structures, CAD is hosted on a data center and the results are stored there. The user is allowed to download the results or make them publicly available. Cloud structures are more efficient due to the lack of the need to purchase and install CAD systems at workplaces, access from a browser or network device, but users have security issues. Application servers can interface with real hardware. Application servers and methodical server are located on the virtual machines of the SibFU data center and are accessible on the Internet. This provides an environment for interactive online learning. Results are sent to users by e-mail or accepted by the user. In cloud structures, CAD is hosted on a data center and the results are stored there. The user is allowed to download the results or make them publicly available. Cloud structures are more efficient due to the lack of the need to purchase and install CAD systems at workplaces, access from a browser or network device, but users have security issues. Application servers can interface with real hardware. Application servers and methodical server are located on the virtual machines of the SibFU data center and are accessible on the Internet. This provides an environment for interactive online learning. Results are sent to users by e-mail or accepted by the user. In cloud structures, CAD is hosted on a data center and the results are stored there. The user is allowed to download the results or make them publicly available. Cloud structures are more efficient due to the lack of the need to purchase and install CAD systems at workplaces, access from a browser or network device, but users have security issues. Application servers and methodical server are located on the virtual machines of the SibFU data center and are accessible on the Internet. This provides an environment for interactive online learning. Results are sent to users by e-mail or accepted by the user. In cloud structures, CAD is hosted on a data center and the results are stored there. The user is allowed to download the results or make them publicly available. Cloud structures are more efficient due to the lack of the need to purchase and install CAD systems at workplaces, access from a browser or network device, but users have security issues. Application servers and methodical server are located on the virtual machines of the SibFU data center and are accessible on the Internet. This provides an environment for interactive online learning. The results are sent to users by e-mail or accepted by the user. In cloud structures, CAD is hosted on a data center and the results are stored there. The user is allowed to download the results or make them publicly available. Cloud structures are more efficient due to the lack of the need to purchase and install CAD systems at workplaces, access from a browser or network device, but users have security issues. In cloud structures, CAD is hosted on a data center and the results are stored there. The user is allowed to download the results or make them publicly available. Cloud structures are more efficient due to the lack of the need to purchase and install CAD systems at workplaces, access from a browser or network device, but users have security issues. In cloud structures, CAD is hosted on a data center and the results are stored there. The user is allowed to download the results or make them publicly available. Cloud structures are more efficient due to the lack of the need to purchase and install CAD systems at workplaces, access from a browser or network device, but users have security issues.

The program-methodical complex allows you to describe many technical solutions in the form of formalized tasks at various levels of abstraction. Formalized tasks in high-level universal languages are unified in various syntax environments C ++, ADA, PLI, JAVA. Dialogue debugging of formalized tasks, automated analysis with comparison of estimated and actual results, as well as automatic resource assessment and documentation of results are provided. With satisfactory analysis results, many technical solutions or optimal structures can be transferred to industrial CAD systems PCAD, ALTIUM, (PADS Mentor Graphics), ORCAD, CADDY, (EAGLE, REVIT Autodesk), (CADSTAR Zuken), CATIA and PRAM 5.3. Examples of specialized cloud-based CAD systems are EasyEDA; Integrated Autodesk InfraWorks, Autocad 360, Fusion 360, Onshape [115].

Industry norms and rules are used in specialized CAD systems by industry, despite their changes over time due to the development of materials and technologies. In complex CAD, everything is much more complicated, and more time is required for the real use of rule systems (set of rules-SP). The development of Internet-based devices (IOTs) based on systems on a chip should facilitate the assessment of the status of all components and the use of rule systems in CAD.

Examples of an energy-efficient data transmission system for IOT are LPWAN and NB (teleofis.ru).

The software-methodological complex UI CAD <COD> is presented on an optical disk (DVD ROM), on university servers with network access (e.sfu-kras.ru), contains client and server versions for Windows, Linux, OS/2 and posted in the public domain in the library of the Siberian Federal University (bik.sfu-kras.ru).

The work was carried out in the laboratory of heterogeneous computing systems of the Department of Computing Engineering of IKIT SFU, used in classes and in the computer center of the Institute of Space and Information Technologies (IKIT) of SFU, and in the computer data center of the Siberian Federal University. The data center virtual machines host teaching materials (e.sfu-kras.ru) and personal dashboards for employees and students, as well as application servers for performing formalized tasks of projects in various environments with a large number of examples: CODWIN for Windows, CODLIN for Linux, CODOS for OS/2-EcomStation [50-57].

This work was supported by the Ministry of Education of Russia by order of 195 dated 16.3.1987 "Creation and development of educational and research software and methodological CAD complexes (UI PMK CAD) in universities". Clause 3.2.17 of Order 195 approved the author's work on PMK UI CAD CAD heterogeneous computing systems (PMK UI CAD CAD NVS). The complex is continuously developed by the author and is supplemented by the best projects of IKIT SFU students, carried out under the guidance of the author.

Requests for the contents of the book and the complex can be sent Professor B. I. Borde by email: bborde@sfu-kras.ru.

#### 1. DEVELOPMENT OF COMPUTER SYSTEMS AND MEANS FOR THEIR MODELING AND DESIGN

#### 1.1. The development of heterogeneous computing systems

Consider the main types of computers and the stages of development of information technology. According to the methods of presenting information, computers are subdivided [1, 2, 6, 140] into analog (AVM) [140], digital (digital computers) [91] and analog-digital (ADC) [53, 111, 129, 141]. In the analogue representation, the result corresponds to the signal value, the error is determined by the components and the level of interference and increases during the calculation process, as well as during storage and transmission of information in analog form over communication lines. Therefore, with the analog representation, all operations are performed simultaneously and are limited in space, the time for solving the problem does not depend on its complexity. However, the amount of equipment and cost are proportional to the complexity of the task.

In digital representation, the result corresponds to the state of many elements; each element can be in different, resistant to interference states. Elements with two stable states provide the highest noise immunity and low switching energy [35, 36, 125, 142, 144, 148]. The value of the threshold signal and the voltage of the energy source are determined by the level of interference. In digital computers, elements of logical operations and information storage are implemented. However, the error in performing calculations and data storage decreases with increasing number of bit elements. The transmission of information in digital form does not increase the error. Therefore, the digital computer sequentially performs operations on stored data. However, the simultaneous execution of operations on the data stream is carried out only in conveyor computers. The digital form of presentation of information made it possible to create an evolving global network of computers and network service centers (DSS) or data processing centers (DPC) [4, 5, 157, 158, 159].

At the first stage, due to the lack of general communication the user group systems ran on the same machine. The virtual machine system [5, 28–33, 86, 92] made it possible to provide an individual environment at the workplace due to a specialized communication subsystem with the ability to exchange messages. Specialized network services became available with the advent of data processing and transmission systems based on a virtual machine system. The complexes connected by the data transmission network allowed employees to receive specialized computing and educational services [86].

Personal computers with local communication subsystems made it possible to install software at the workplace and solve the required tasks. The effectiveness of personal computing systems was limited by the qualifications of users, high energy consumption and high cost of ownership.

The combination of personal computers with global communication systems [91, 100, 107, 157] and service centers made it possible to raise the quality of information systems. Software is installed at the workplace to solve

basic problems, and additional tasks and information retrieval are performed in the form of network services. The cost of ownership has decreased with increasing quality, but a qualified specialist is required for management. The increase in the number and complexity of computing and communication systems in all areas of activity has become limited by the number and qualifications of personnel.

Personal computing facilities are divided into stationary and mobile [4]. Stationary are located at workplaces and have a wired connection to the network, their speed and power consumption are constantly increasing, they are necessary for developers and professional users. Despite the effectiveness of stationary terminal machines (thin clients), they are not widespread.

Mobile personal equipment is represented by portable computers – MPC, tablet – TPC, telephones and communicators with a wireless connection to a data network. Increasing the degree of integration of the main components of data processing and transmission has allowed the creation of mobile Internet devices (MID) and ultra-mobile personal computers – UMPC, for example, Computer Card from Intel. Mobile network devices and computers are software compatible with personal computers, and monitor sizes average between monitors of tablet computers and communicators. Mobile tools are optimized not only in terms of cost per unit of productivity, but also in energy consumption. One of the main parameters is the operating time from an autonomous power source. Specialized systems on a chip (SOC) have been developed for mobile devices. The chip contains analog-to-digital and digital components and sensors, the connections of which are programmed and can be changed dynamically (PSOC). Examples of PSOC are INTEL D1000, D2000 crystals. Mobile users and affordable servers form a dynamic computing and communication system. Limited mobile computing and energy resources stimulate the use of network services that meet standards and are not dependent on a hardware or software platform [4]. Network services are performed at data centers combining computing resources, storage facilities, uninterrupted power supply and cooling. Virtualization can improve the efficiency of data centers [4, I6, I8, I24]. The main ones are the quality parameters and the reliability of the services provided.

Personal and mobile means of data processing and transmission allow today to receive online educational and computing services at any time at the workplace and at home [4].

#### 1.2. Abstraction levels of computing systems

Design decisions are models of objects at various levels of abstraction. The initial stages of design [100–105] are distinguished by a high level of abstraction, which decreases with the specification of the structure and parameters of objects.

The following stages of design and maintenance of the life cycle of objects are known: the goal of creating and evaluating the effectiveness, conceptual, functional, design, technological, testing, maintenance and disposal of objects [28–33, 103, 104].

Different stages of design correspond to various descriptions of objects and criteria for their effectiveness. Distinguish the content and syntax of descriptions. The content of the descriptions is determined by the subject area and the design stage. The variety of descriptions is explained by their syntax, not content.

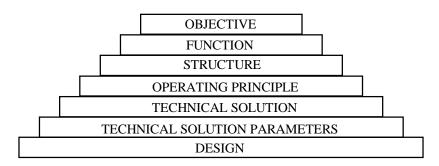

At the upper level of abstraction (fig. 1.1), functional models of systems as a whole are considered, which are called macro-models and are described by the functions of outputs and transitions. In various CAD systems, functional models of systems are presented in various forms and in different languages.

At the next level of abstraction are structural models that reflect the internal structure of components. Such models will be called micromodels. At this level, one can roughly estimate resources: mass and dimensions, static power and switching energy, thermal characteristics, external environment and cost [1, 2, 6, 9, 11, 27–33, 87, 101].

Fig. 1.1. The hierarchy of technical solutions at various levels of abstraction

The same structure can be implemented using components with different operating principles. It is possible to compare options from components with different operating principles. The processing subsystem can be implemented on some physical principles, and the communication one on others. The physical principles of the action of computer elements are described in detail in [1, 6, 8, 9, 16, 19, 20, 21] and will be considered only when assessing resources or optimization [95, 96, 124, 125].

Knowing the principle of action, taking into account the level of technology and technology, you can go to the level of technical solution. The technical solution should be feasible. After receiving the technical solution, it is possible to change the parameters of the solution in order to improve the quality of the product. Such examples are considered in the author's works on parametric optimization [12–15, 34–38].

Having determined the parameters of the technical solution, they proceed to the system design. For example, depending on the power dissipated by the crystal, an appropriate package will be assigned to it. The design is significantly affected by the external environment (operating conditions). Thus, at the upper level of abstraction are functional models of the components, and at the lower level are the structures of the components and their geometry. Geometric models of components are used in the construction of [101].

Design solutions for computing devices and systems at different stages of design represent many components and relationships. Relations can be of the type of affiliation (corresponding to the list of elements included in the device) or the transmission of information through channels. Relationships vary in content and presentation. The main thing is the content of the relationship, and the presentation form allows for many implementations that are limited by industry standards and specific CAD systems. International standards ISO 10303 and EDIF, PDIF define the protocol and data exchange structures between various CAD systems [128, 130, 133, 134].

There are problems of parametric [95, 96, 112, 124, 149] and structural optimization [3, 17, 27, 28, 60–63, 71, 83, 88, 102–105, 110]. In parametric optimization, controlled parameters corresponding to the extreme range of the output parameter are estimated [15–19, 34–38]. During structural optimization, many structures are synthesized, from which the best according to the quality criterion are selected [103]. Structures differ in components or component relationships. For computing systems, a relationship can be represented by a common data channel in the form of a connection for stationary components and the ability to exchange messages for mobile components.

In the table 1.1 shows the main levels of abstraction of heterogeneous computing systems and criteria for their effectiveness. The models for each level are independent, however, in the transition to nanotechnology [59], the logical, physical, and spatial levels of computing systems are dependent and affect the result; therefore, a number of iterations are necessary taking into account the dependent levels.

Table 1.1 NVS abstraction levels

| № level | Abstraction                                      | Level                 | Name performance criteria                                                                      |

|---------|--------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|

| 7       | Processing method of information                 | System complex        | Perfection of an energy or substance conversion system in an unsteady environment              |

| 6       | Information Processing System Structures         | End result            | Efficiency of energy or substance conversion in information processing                         |

| 5       | Internal structure                               | System<br>Information | Perfection Information<br>Transformation System                                                |

| 4       | Logical implementation of information converters | Structural            | Perfection of the structure – the number of ticks for processing an application for an element |

| 3       | Physical feasibility                             | Logical               | Perfection of logical information converters                                                   |

| 2       | Spatial placement                                | Physical              | Switching operation complete                                                                   |

#### Continuation of the table 1.1

| 1 | Processes in a heterogeneous environment | Spatial                            | Bulk (surface) density         |

|---|------------------------------------------|------------------------------------|--------------------------------|

| 0 | No                                       | Inhomogeneous physical environment | Permissible working conditions |

At the systemic integrated level (7), the efficiency of energy or substance conversion is evaluated with or without a structure that processes information. At the level of the final result (6), the perfection of the information processing structure is evaluated. At the system information level (5), the perfection of the information processing transformation system is assessed with the abstraction of its internal structure. The structural level (4) is estimated by the number of ticks for processing an application for an element.

The logical level (3) is characterized by abstractions of the spatial distribution of components and their physical implementation. However, when coordinating a computing system (BC) with external channels, it is necessary to specify the physical implementation of the components. At the physical level (2), the state change energy for the binary component is estimated – the switching energy, which determines the power dissipated by the object for a specific frequency and limits the degree of integration of the components [69, 84, 99, 125, 142]. At the spatial level (1), the arrangement of elements tends to the maximum volumetric or surface density of the components, limited by technological standards and allowable power dissipation. Spatial placement is taken into account only in the design of objects with stationary components [6, 120–123].

The appearance of components with medium and high degree of integration has led to the need to create BC models that are heterogeneous in terms of abstraction. For example, in the BC model based on a microcomputer for signal processing, external digital or analog signals must be represented in a multivalued alphabet. The level of representation of internal processing components is similar, up to interface nodes that act as converters of levels of abstraction of signal representation [33, 118, 138]. If the protocols of signal transformations inside the microcomputer are standard, then there is no sense in their detailed analysis and you can go to a higher level of abstraction. Therefore, BC models that are heterogeneous in levels of abstraction are needed.

The process of designing and testing a new facility is iterative (fig. 1.1). In each iterative cycle, design procedures for the synthesis, analysis, and decision-making are performed. The decision analysis procedure for known components is carried out automatically, and the synthesis and decision-making are implemented by an engineer or student.

The result of the synthesis is a description of the object, the result of the analysis x evaluation of characteristics and a diagram of the behavior of the object under certain external influences.

For simple objects, the analysis of behavior is simpler than its description, however, with an increase in the complexity of objects, the analysis of behavior becomes a very difficult task compared to its description. Therefore, the automation of analysis should be ahead of the automation of the synthesis of computer systems.

The iterative process is controlled to obtain a description of the object, the characteristics and behavior of which satisfy the task. You can control the description of the object obtained as a result of synthesis, and external influences on the object.

The purpose of creating a system or device is the final results obtained after the implementation of objects, which should fulfill the functions at given intervals of change in destabilizing factors. The formation of the technical task completes the stage of external design [48, 60–63].

#### 1.3. The development of heterogeneous computing systems

When performing work on test automation and technological processes, it was necessary to find the optimal distribution in the space of programmable devices for interfacing with objects [42, 43, 44]. The analytical cost model allowed us to find a solution.

Microcomputers make it possible to implement multifunctional active devices for interfacing with objects (IWO). The accumulation of knowledge and models of processes and signals involves entering the deviations of the signals from the expected ones and setting the boundaries of the operation intervals according to a certain algorithm [17, 29, 72, 84, 85, 155, 156].

The proximity of active IWO to objects can reduce the level of interference at the input of devices and increase the information performance of the entire system. However, the distribution of IWO in space leads to an increase in hardware costs. The optimal distribution of IWO in space is determined by the level of development of the element base, from microcomputers with analog-to-digital devices to systems on a chip (SOC) [42–44, 58].

The optimal distribution problem in the IWO space on the basis of a microcomputer was solved [42–44] using the relative cost model that provides acceptable reliability of the results. For the time of physical and moral aging of TAM equipment and the time of existence of the structure of the TAS subsystem (estimation of the average time interval between tunings), an estimate is obtained of the optimal number of active IWOs based on NPUCO microcomputers and the optimal number of signals for IWOs – NCO. An informative parameter is the total relative cost of IWO for the entire life of the system:

$$KCUS = 2 * ((TAS / TAM) * CKUCO + TAS * CTUCO) / (CPLA * (LA + LB)),$$

$$(1.1)$$

where CKUCO, CTUCO – capital and operating costs for IWO on the basis of microcomputers; CPLA – linear cost of analog highways; LA, LB – geometric dimensions of the object.

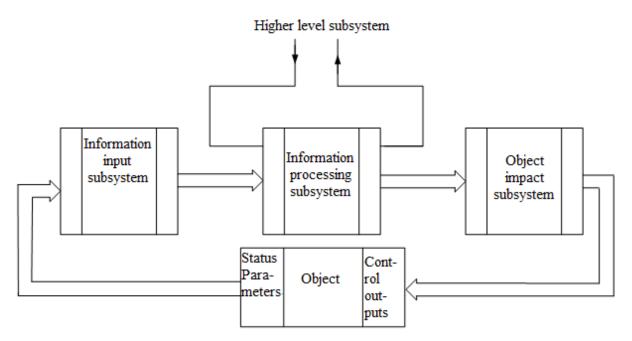

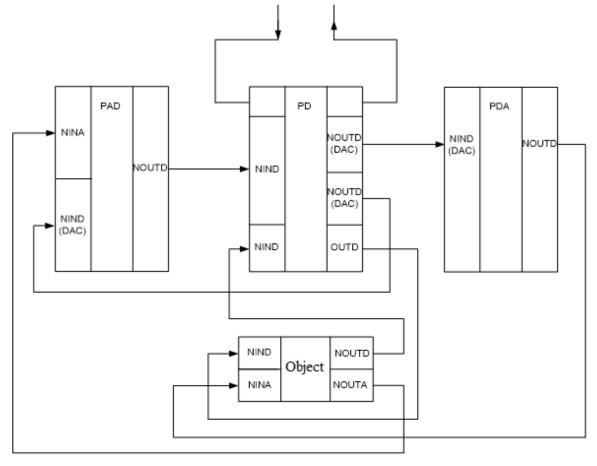

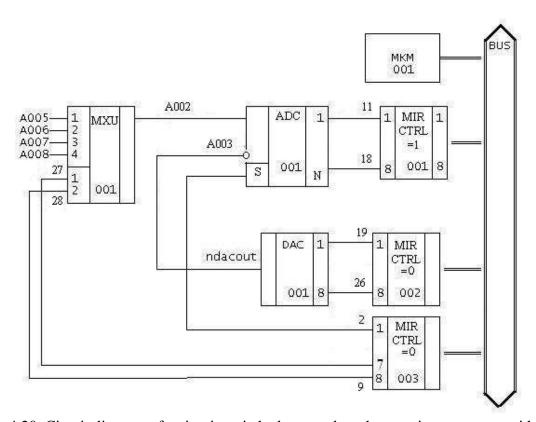

Fig. 1.2. The structure of the active device pairing with the object

Fig. 1.3. The structure of the active device for interfacing with an object with digital-analog and analog-to-digital subsystems: PD – digital processor, PAD – analog-to-digital processor, PDA digital-to-analog processor

Dependencies of NPUCO and NCO on the number of NCS signals, the KCUS parameter, and the relative cost of digital highways, taking into account the nature of the IWO with the next hierarchy level (coefficient KS) is determined by the expressions

$$NPUCO = \sqrt{\frac{NCS}{\frac{CPLD}{CPLA \cdot KC} + KCUS}}$$

(1.2)

and

$$NCO = \sqrt{NCS \left(\frac{CPLD}{CPLA \cdot KC} + KCUS\right)},$$

(1.3)

where CPLD is the linear cost of the digital highways.

The results of calculations by formulas (2) and (3) are presented in an interactive graph in [28, 29]. Thus, with a decrease in the cost of IWO on the basis of a microcomputer, the degree of their distribution in space should be increased. The limiting factor is the relative cost of digital highways. Reducing the average interval between system adjustments increases the degree of distribution of IWO in space. The distribution of the signal conversion and processing subsystem based on the microcomputer is cost-effective, despite the increase in the cost of equipment, which is confirmed by the results of the development and implementation of such subsystems. In the near future they will be replaced by wired or wireless systems on a chip (SOC) [58, I3, I8].

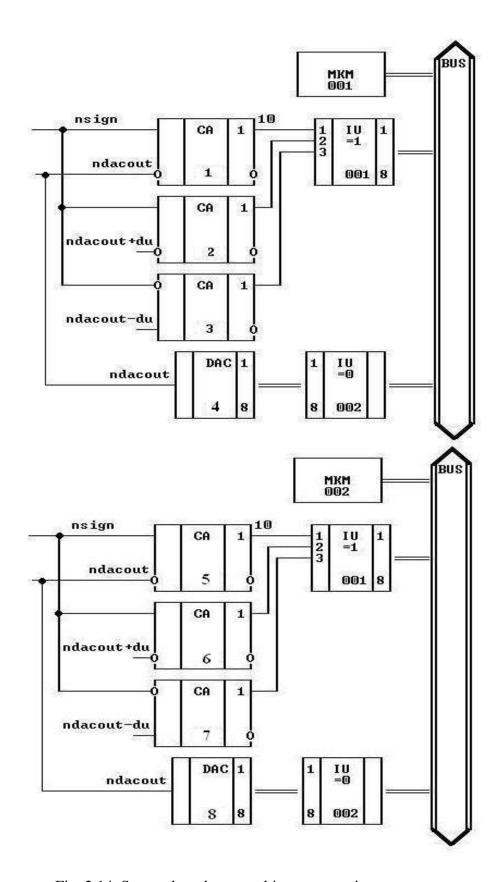

In fig. 1.2 shows the structure of an active device for interfacing with an object [2, 3, 28, 29], many of which are distributed in space and work simultaneously. Figure 1.3 shows the generalized structure of an active device for interfacing with an object with subsystems of digital and analog signals [2, 3, 28, 29]. The output subsystem (PDA) converts groups of digital signals into analog ones and consists of two parts. The first is fed to the object and depends little on the algorithm of the digital subsystem. The second part is fed to the input subsystem for converting analog signals to digital (PAD) and, as knowledge about the object accumulates, it corresponds to the expected analog signals. A digital processor (PD) may contain the required number of cores, depending on the complexity of the object model.

# 1.4. Complexes of modeling and design heterogeneous computing systems

One of the first computer-aided design systems was CASPI [9], created under the leadership of S. A. Lebedev, B. A. Babayan and G. G. Ryabov. KASPI implemented a subsystem for modeling logical circuits, levels of physical and

spatial placement of components, tracing and preparation of data for technological equipment.

In 1970-1990 years, The Ministry of Education coordinated and supported the development of research software and methodological complexes for modeling and designing computational and test systems [29, 101, 102, 135, 137, 138, 139]. Most of the work related to the logical and circuit levels with specialized project description languages, similar to the well-known foreign modeling system SPICE [103]. The main program and methodological complexes were created under the guidance of I. P. Norenkov [102, 135], E. I. Artamonov [2, 3], V. I. Anisimov [139], V. M. Dmitriev in Tomsk [7], V. V. Toporkova [137, 138] and A. K. Polyakov [114, 115]. The Ministry of Radio Industry developed the PRAM (RAPIRA) complexes under the leadership of Yu. Kh. Vermishev [86, 128], of which we used PRAM53 together with PRAM2, PRAM53M / PC97, of PCAD-200X **GRIF-4** [779], (development in NPO DIAMOND) Yelshin Yu. M.

In the process of developing computer systems and increasing the degree of integration of microcircuits, modeling and design complexes became specialized for microchip developers [1, 132] and for system integrators [8, 103, 114, 115]. Complexes for system integrators, to which we pay the main attention, along with the logical level, over time had to solve problems of the structural and system level. If in existing complexes the main input of information is graphic and does not require knowledge of programming languages, then in the future the main input of information will be textual or interactive, in universal languages for describing systems with additional libraries.

Modern complexes of modeling and design are represented by commercial and free products [58, 116]. For systems on a chip, the main task is to create an "executable system model" corresponding to a formalized task put into practice by V. M. Glushkov. Consider the complex "Visual Elite" by Mentor Graphics and "Riviera Pro" by Aldec. The main project description language is the IEEE std standard adopted in 2005. 1666-2005 SystemC [I23]. It is proposed to use the standard C language (C ++) with restrictions and additional libraries. Along with the standard, the use of VHDL fragments (a subset of the ADA language for describing digital systems) and the input of graphic fragments are allowed. For macro programming in CAD, NETScriptCAD is adopted.

The use of graphical fragments does not allow us to describe in a single formalized task many design options and move on to the second level of complexity of design problems [103]. The complexity of the complexes with the description in one main language on one platform does not exclude system errors at a high cost of the product.

Free CAD can be attributed to two groups. The first group allows you to abandon the commercial products of circuit design and engineering design (Kicad, gEDA, FreePCB, Electric) and is suitable for the technical design of one or two options for the object. The second group of free products is being developed by an international consortium based on standards, thanks to Internet technology, as an extension of the international tool project Eclipse [I4].

Thus, the existing systems of modeling and design do not allow to proceed to the solution of design problems of the second level of complexity while increasing or maintaining labor productivity. Complexes on the same platform with descriptions in one main language do not exclude system errors. There is no automatic conversion of formalized task options into a schematic diagram and a three-dimensional model with the display of signals at the early stages of design. There is no abstract type of components.

The necessity of solving the urgent problem of creating an open modular multilevel software and methodological complex for multivariate modeling and designing heterogeneous computing systems with the introduction of a formalized set of many options and the automatic formation of diagrams, schemes, three-dimensional appearance of the object and the assessment of its basic parameters in various syntactic environments and on various platforms is shown.

It is necessary to increase labor productivity in multivariate design and in the learning process by automating the formation of models and documents [233].

The author has proved the tendency of the optimal distribution of analog and digital data processing in space by approximating the means of analog-digital processing to the sources and consumers of signals in the process of development of computer systems. In the limit, when switching to systems on a chip (SOC), analog signals are processed directly at the sensor, and data is transmitted over a serial digital network. In the production of large batches, specialized SOCs are used, containing even sensors such as DS18B20 from Dallas, and later from Maxim. For small batches, PSOCs containing digital and analog subsystems, input and output communication subsystems produced by Cypress Semiconductor in conjunction with the programming environment are effective PSoC Development Tools.

Since 2018, we have been using a system on an Intel D2000 chip as a debugging module in conjunction with Intel System studio.

# 2. PRINCIPLES OF CONSTRUCTION OF MULTI-LEVEL MODELING SYSTEMS AND PROJECTIONS COMPUTER SYSTEMS

#### 2.1. Description of design solutions for computing systems

Design decisions are models of objects at various levels of abstraction. The initial stages of design [1, 9–12, 89, 93, 95, 103] are distinguished by a high level of abstraction, which decreases with the specification of the structure and parameters of objects.

At first, the object is represented by a functional macromodel, then the object is represented by a micromodel of abstract functional components. Abstract functional components are represented by micromodels of abstract or specific functional components. The process continues to the level of specific functional components for which it is possible to evaluate the resources of creating objects.

I. P. Norenkov distinguishes design tasks by difficulty level [102, 103]. The first level of complexity includes tasks in which technical solutions are given and there is no synthesis. The second level of complexity is distinguished by many possible technical solutions in the presence of resources for analysis, evaluation and selection of the best option according to the efficiency criterion. The third level of complexity [103] includes tasks with many possible technical solutions with a lack of resources for analysis and evaluation of all possible options, so some of the options have to be excluded without a detailed analysis. Thus, tasks of the third difficulty level are transformed to the second.

Computer-aided design occupies an intermediate position relative to traditional (manual) and automatic design.

When designing aircraft, state standard R ISO 10303, introduced on July 1, 2000, provides for the generation of product information to supplement it during production, operation, maintenance and disposal [29, 33, 79, 104, 133]. Information can be used in computer systems in various organizations. Product descriptions must be complete and compatible.

The description of computing systems consists of models of components and connections between them. It can be represented in various ways. When describing the system in the form of a formalized task, the "Components" and "Connections" sections are sufficient.

A computer system as a design object is represented by a set of interacting components, each of which can be considered as a composite object. The model of an abstract object is represented by a data structure whose value reflects its state by methods or operations that transform the states of objects in accordance with perceived input messages. The object model generates output messages or procedure parameter values for other objects. Important for human perception is the form of representing objects and taking into account exceptional situations. Known symbolic, tabular and graphical forms of presentation. The behavior and interaction of objects is perceived better in graphical form (timing diagrams and circuit diagrams). These are the concepts for describing and representing the

subject area of heterogeneous computing systems. A formal representation of a subject domain (PRO) is possible using ontologies [10, 70]. The ontology model is represented as

$$O = (T, TREL, FVIEW),$$

where T is a finite set of concepts (concepts, terms); TREL - a finite set of relationships between concepts; FVIEW is a finite set of interpretation functions defined on concepts or relationships.

The basic concepts in the field of information technology and automated systems are given in GOST 34.003–90. The concept of functional components and the corresponding symbols on the circuit diagrams are defined in the ESKD standard GOST 2.743–91, and the concept of "product model" in GOST 2.052–2006. The relations between functional components (TREL) constitute a computational module, which can be considered as part of a formalized task (FT), a module description section (UNIT) and presented (FVIEW) as a circuit diagram or volumetric model [29, 32, 33].

The use of ontologies in the design and maintenance of objects is recommended by the Russian standard R ISO 15926, adopted in 2008. Due to the large number of specific components and terms, a multi-level model with a small number of basic concepts at the top level is used. As the working conditions of the object are clarified, the components are specified and their diversity increases. Multilevel presentation allows you to even out the complexity of decision-making at various levels.

International standards ISO 10303 define the protocol and data exchange structures between various CADs [103–105, 115, 133] and object tracking systems. An example of a standard for describing digital systems (VHDL) [8] is the document of the Institute of Electrical and Electronics Engineers (IEEE) No. 1076. The VHDL language is based on the universal algorithmic language ADA. The new edition of VHDL STD 1076.1–1999 (VHDL – AMS) introduced the ability to describe analog signals [132]. In 2004–2008, standards were adopted for the IEEE STD 1666–2005 system-level design language and its development. The lack of a standard leads to incompatibility of representations of design decisions in different CADs with identical contents [1, 31, 84, 104, 128].

The transition to a lower level of abstraction should be accompanied by the concretization of existing descriptions of objects and the introduction of new information in the form of relations. A single entry of information from those sections of the descriptions that are not changed in the subsequent steps is desirable. The description section usually consists of several relationships.

The uncertainty of the structure or parameters of the system [55–58, 65, 67, 90, 97, 155], which is large at the initial stages of design, is subject to specification. Pre-design studies are carried out when only the purpose of creating the system is known, and their result is the technical task (TT). The main part of the TT is a lot of relationships in the form of restrictions, for example: system

performance on a set of tasks no less than given, system cost no more than established, or limit value of a complex criterion cost-performance ratio.

The presence of TT allows you to compile and analyze technical solutions, many of which can be represented in the form of a tree [87, 104, 112] from vertices of type I and OR. Vertices of the AND type determine the necessary composition of the object, and OR vertices determine the indefinite components to be specified by analyzing the consistency of the properties of the component and the object or analyzing the operation of the device.

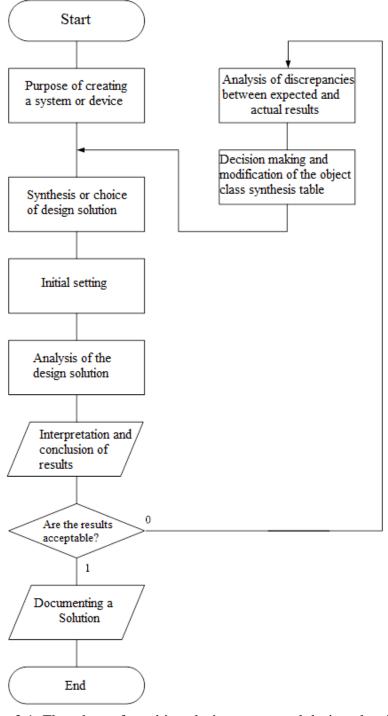

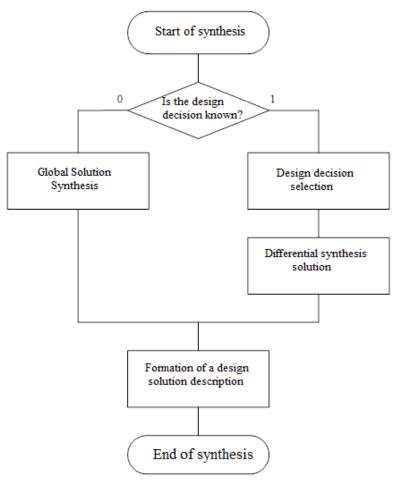

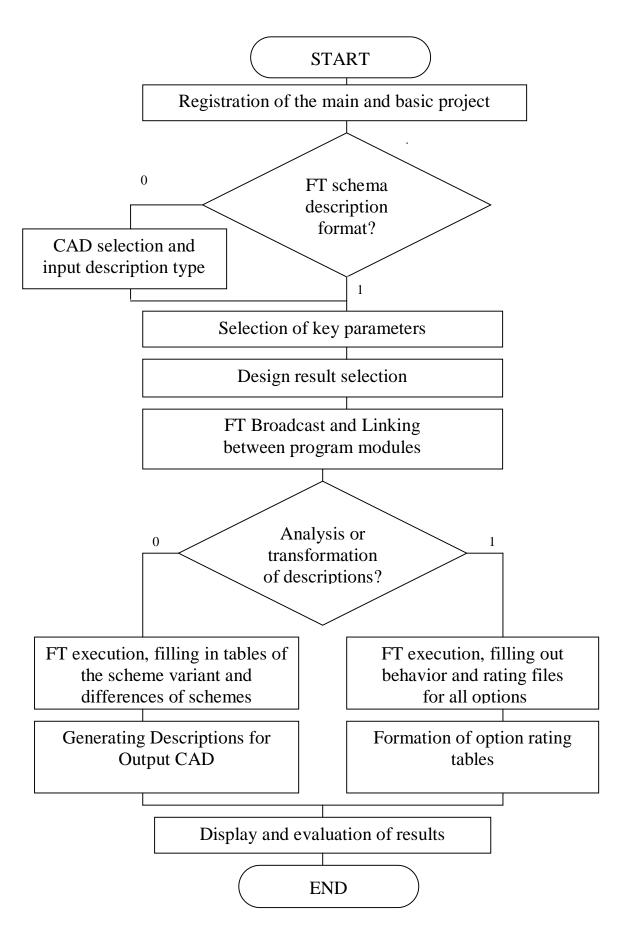

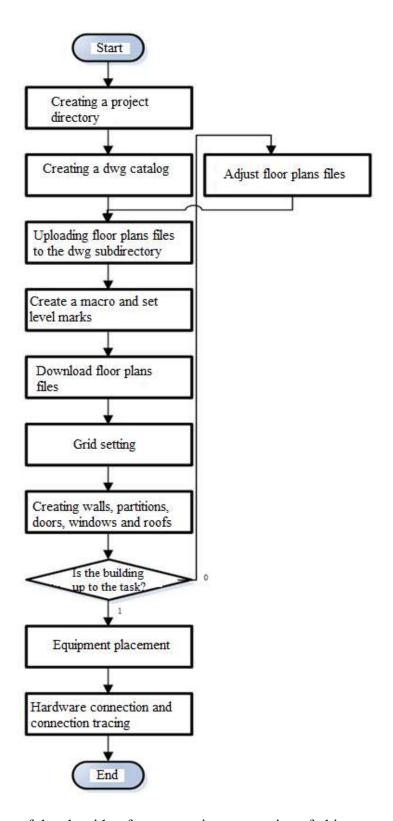

The result of structural design is the composition of the components and the relationship between them. At the stage of technical design, the composition of components and connections should be fully specified. On fig. 2.1 shows the flowchart of the design algorithm for the structure of objects.

The variety of object description rules in various CADs generates many design languages. There are various ways to enter descriptions: from typing to interactive systems with a graphical interpretation of descriptions and analysis results.

External design of an object includes the construction of a macromodel and resource limitation. Internal design includes the creation of micromodel variants with varying degrees of specification of components. At the lower level for specific components, it is possible to evaluate resources and compare various options for an object. Efficiency assessment is carried out only for models of objects for which the output signals correspond to the expected ones.

A feature of computing systems is the choice of the principle of operation for detailed functional diagrams. The principle of operation is selected depending on the working conditions and the external environment.

The process of obtaining a detailed micromodel of an object is called a <design route>. Unlike the algorithm, the design route may not be completed in a finite number of steps. The design of the object is carried out by the iterative method with training at each iteration. The brief synthesis and interpretation operations are performed by the engineer, and separate simple operations and labor-intensive analyzes are subject to non-availability. To automate the following stages of the design of the computing devices and the system of the results of the structural synthesis must be presented in a view from the window.

Spatial placement of structural components and coefficients is carried out at the design stage of the design. Component geometry models are stored in the general or local data base.

Multilevel CAD COD (Conceptual Object Design) is used to synthesize and analyze many variants of structures and automatically convert them to many design solutions for industrial CAD [12, 27, 32, 33].

To make a decision and synthesize objects in the COD software and methodological complex from a multivariate object-component formalized description of objects (FT), time diagrams are generated with automatic comparison of estimated and actual signals, tables of parameters and optimality criteria, circuit diagrams and images of objects for all options. Component designs

may display digital signals and temperature. To move to technical design, the Federal Law is converted to the format of a specific design system.

Analysis of the discrepancy between the expected and actual results allows us to make a decision on the modification of the rules for the synthesis of a class of objects. Synthesis rules are represented by a decision table and can be described in a formalized task using conditional operators or selection conditions.

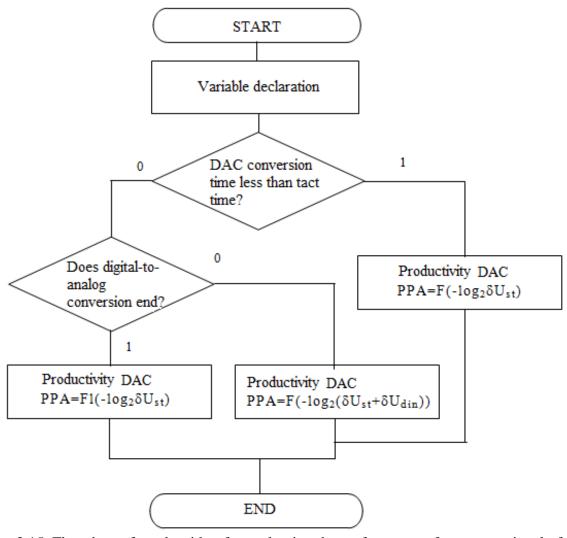

Performance is determined using tests: on useful work performed per unit of time or on changing a digital or analog signal over a given time interval [32, 33, 132, 148]. When evaluating performance, the number of the changing digital (nppd) or analog (nppa) signal is set.

Fig. 2.1. Flowchart of an object design automated design algorithm

Fig. 2.2. Design decision synthesis flowchart

The minimum volume of the description of the object is presented in symbolic form, and the maximum – in graphic form. Therefore, the input of symbolic descriptions and the automatic conversion of descriptions into forms convenient for human perception are distinguished by the minimum complexity.

The description of the structure of the object is related to the results of internal design, which can be performed by various methods. If the design solution that meets the requirements of the assignment is unknown, then the basic procedure for synthesizing a description of a new object is performed. If there is a design solution required or close to it or a plurality of solutions, it is selected and, by making changes to the structure of the object, they achieve the requirements of the technical task. Methods for the synthesis of solutions are shown in fig. 2.2. Procedures for the examination of technical solutions for novelty require the identification of similar solutions and evidence of the significance of differences, which confirms the need for the chosen direction of differential synthesis and analysis.

When describing many decisions in a low-level language, the number of descriptions is equal to the power of many decisions, and when describing in high-level languages in one description there can be many solutions. Rational is the description in a high-level language of many solutions for one class of computing systems or devices.

For structural optimization, performance criteria are needed [33, 90, 93, 95, 96, 124, 125]. For stationary computing systems, the criterion of efficiency is the cost of a unit of performance. For mobile objects, such a criterion may be the mass of a unit of productivity or the mass of a computing system and an energy source per unit of productivity [29–33]. Such estimates for many solutions represent a complex and time-consuming task, the real solution of which requires tools and information support. Often a limited number of criteria are used, the expressions for which are summarized in table 2.1.

Table 2.1 The main criteria for the optimality of computing systems

| Criteria                          | Dimension           | Expression                                                           | Application area   |

|-----------------------------------|---------------------|----------------------------------------------------------------------|--------------------|

| Unit Cost                         | Relative Cost /     | / K = C / P                                                          | General Purpose    |

| Unit Cost                         | MIPS                |                                                                      | Computing Systems  |

| Unit waight                       | g / MIPS            | K = M / P                                                            | Onboard Computing  |

| Unit weight                       |                     |                                                                      | Systems            |

| Power and mass unit W/MIPS·g/MIPS |                     | $V = M / D \cdot DE / D$                                             | Portable computing |

| of productivity                   | w / Miles g / Miles | $\mathbf{K} = \mathbf{M} / \mathbf{F} \cdot \mathbf{F} / \mathbf{F}$ | systems            |

The heterogeneity of computing systems is associated with various carriers and forms of presentation of information from multiple sources, receivers, and various structural organizations of processing subsystems with a wide range of performance [2].

For flexible automated productions and workstations, the functions of computing systems can be controlled by events, which requires dynamic restructuring of the structure. The joint use of processing and data transfer tools allows you to create dynamically controlled structures of information systems.

The operating conditions of computer technology differ significantly at different levels of the hierarchy. At the top level of the hierarchy are data centers [I6, I8, I14, I24]. Data centers are computing and communication resources with an information storage subsystem with autonomous power supply, climate system and security system. Modular data centers can operate in various conditions [I6]. Workstations and personal servers are typically used in the laboratory. Special operating conditions at the upper levels of the hierarchy, necessary for computer systems at the enterprise level, are replaced by laboratory conditions for personal servers and harsh conditions for specialized systems directly at workplaces and as part of technological equipment.

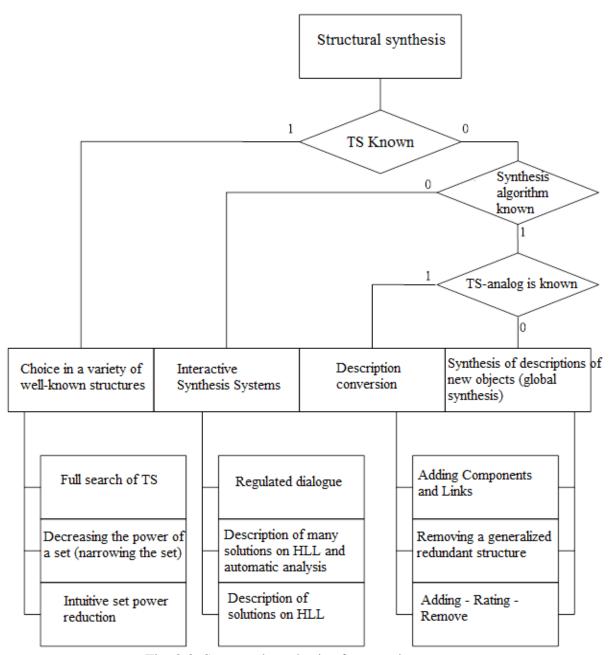

#### 2.2. Structural synthesis of computing devices and systems

Structural synthesis methods [1, 29–33, 102, 103, 132] are presented in more detail in fig. 2.3. If technical solutions (TS) are known and enough resources are available, then a complete enumeration of the options is performed, otherwise the power of many solutions is reduced. For a class of objects, the synthesis algorithm is known and synthesis is possible in the dialogue mode or description

in one of the high-level languages (HLL). An example is the synthesis of a class of roughly accurate analog-to-digital serial count converters [29-33]. A formalized task allows you to get time charts for four options for structures and performance evaluations for fifteen options. The best option was to split the meter into two parts – coarse and accurate.

If the TS of the analogue is known, then differential synthesis is performed by adding and removing a component or links with an assessment of effectiveness. If TS is unknown, then global synthesis is performed.

The structure of the system is determined by many components and the relationships between them. System structures can be static for all variants of the system, static for one variant of the system and dynamically change within any of the variants. Description of the listed structures is possible in high-level languages. In low-level languages, descriptions of only static structures are possible. When changing the structure of the computing system in accordance with the option

$$S(N + 1) = FS(S(N), RS),$$

(2.1)

where S(N + 1), S(N) – structures for N + 1 and N-th version of the system; RS – rules for changing structures depending on the values of the estimated and actual signals, processing results, performance criteria and rules for the class of structures, as well as depending on external influences; FS is the function of forming the structure of variant N + 1.

Fig. 2.3. Structural synthesis of computing systems

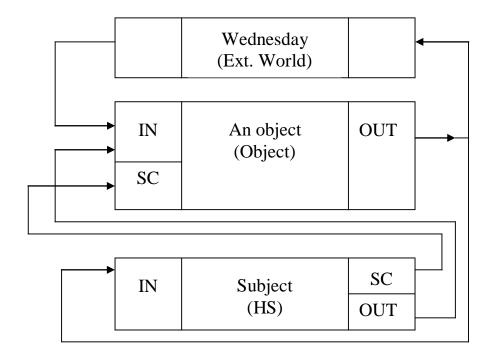

Fig. 2.4. System synthesis procedure taking into account the external environment

The system being created – the object is represented by a finite set of relations between concepts (TREL) [10], and to make a decision about changing a variant, the subject needs to present various properties of the object in visual form, for which interpretation functions (FVIEW) serve. As a result of the design analysis procedure, the object's behavior and resource assessment are obtained. From a formalized task, you can get a diagram in a standard viewer with activity display or a three-dimensional view of a module or system at an early stage of design. Visibility of the interpretation of the results reduces the time of decision making and the formation of synthesis rules [2, 9–11, 55–63].

The external environment is the main factor in choosing the principle of action. Electronic components operate in a limited temperature range and are unstable to many influences. Therefore, it is necessary to consider the principles of operation of analog-to-digital nodes, microcomputer-based systems using the optimal node structure depending on the applications, although in the future you can use a chip system or a signal processor.

#### 2.3. Analog-to-digital devices of computing systems

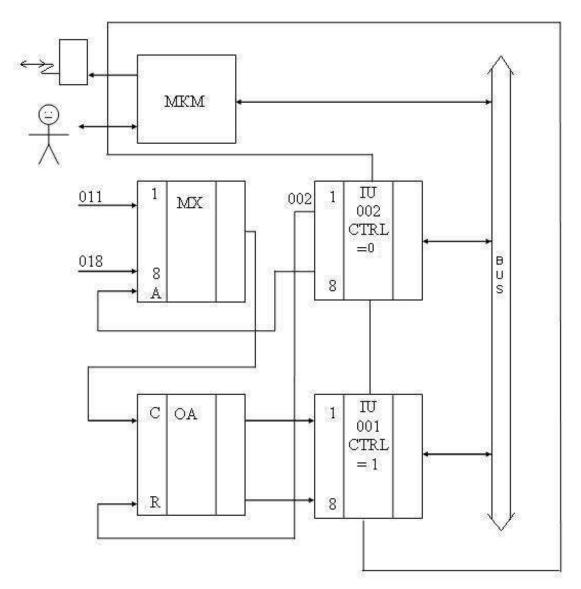

The main nodes of the subsystems for interfacing with objects are analog-to-digital converters (ADC), analog multiplexers, nodes for processing analog signals – analog processors (AP) and digital-to-analog converters (DAC). Analog and digital multiplexers are typical components of computing systems. Their models are included in the component library, and the syntax and semantics tables are given in [6, 33].

As an example of an analog processor, the library includes functional models of an integrator and a scale converter. Along with the analog input and

output, the models contain digital input control signals and a controlled parameter. For the integrator, the controlled parameter is the time constant, and for the scale converter, the transfer coefficient.

The digital-to-analog converter refers to typical components [6, 31]. Functional DAC models have arbitrary bit depth and output signal range. In the table 3.15 shows the main parameters of the converters produced by various enterprises.

Analog-to-digital converters are among the most complex units, including all of the listed components, and are distinguished by structure, speed, error of operation, and resistance to interference. There are [2, 6, 33] ADCs of sequential counting, bitwise and single counting. The former are characterized by minimal speed and minimum hardware costs. The second occupy an intermediate position, and the converters of one reference are characterized by the highest speed and hardware costs. Comparative characteristics of the three types of ADC are given in table 2.2.

Comparative characteristics of the ADC

Table 2.2

| Parameter                                   | ADC Serial               | ADC Bitwise  | ADC                      |

|---------------------------------------------|--------------------------|--------------|--------------------------|

| Farameter                                   | Count                    | Balancing    | single count             |

| Transformation execution time (in measures) | 2 <sup>n</sup>           | n            | 1                        |

| Relative amount of equipment                | 3 · n                    | 4 · n        | $2\cdot 2^n$             |

| C / P Efficiency Criterion                  | $3 \cdot 2^n \cdot DELT$ | 4 (n · DELT) | $2 \cdot 2^n \cdot DELT$ |

In the table 2.2 n – number of bits, DELT – duration of one clock cycle, C – relative amount of equipment (cost estimate), P – performance.

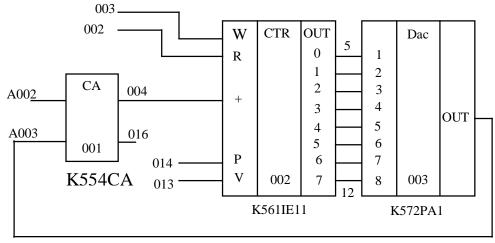

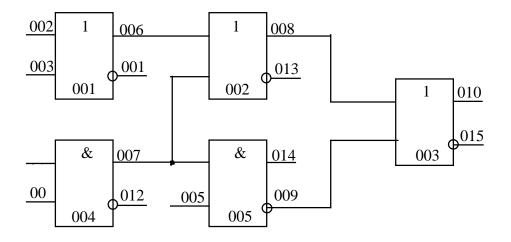

Using a high-level language to describe analog-to-digital devices allows you to simulate analog-to-digital devices with various types of components. For example, in the ADC in fig. 2.5 in different versions, you can use excellent types of comparators.

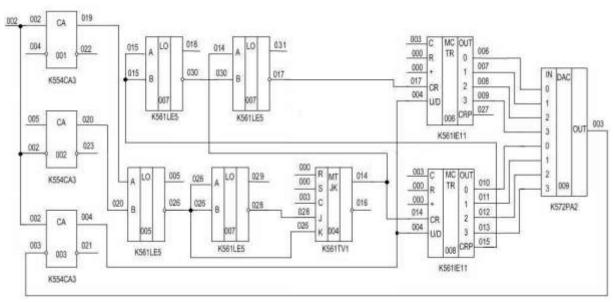

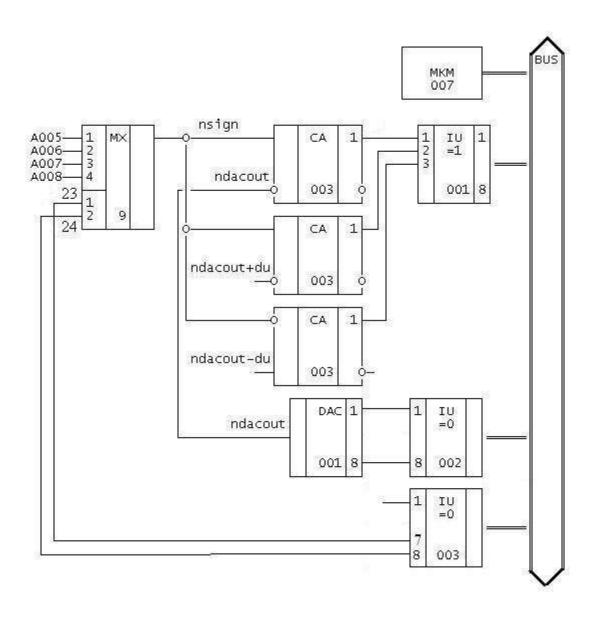

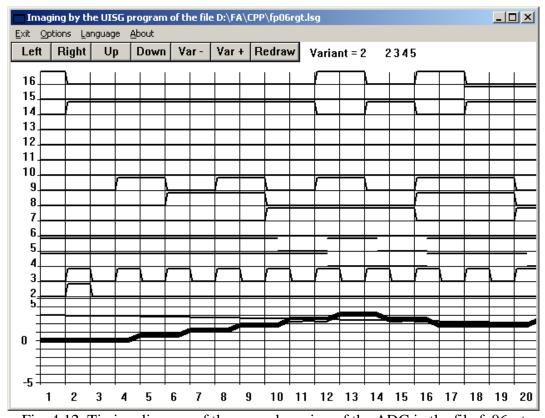

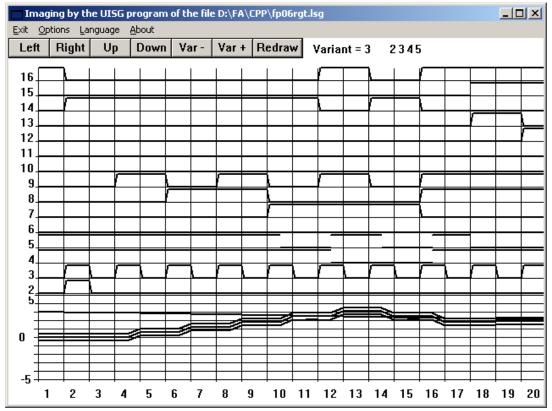

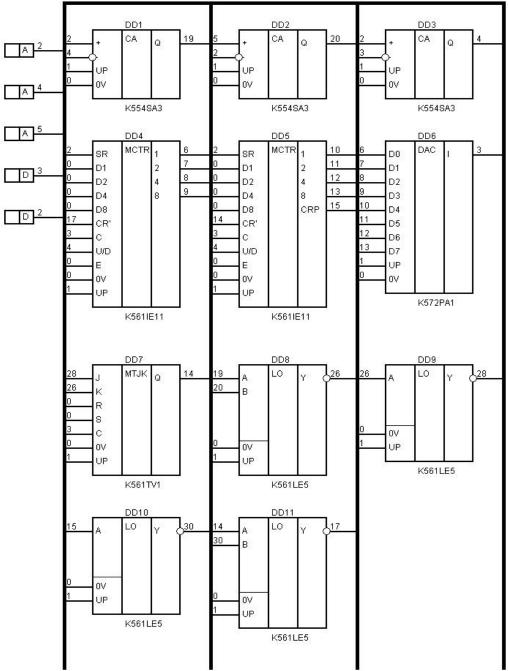

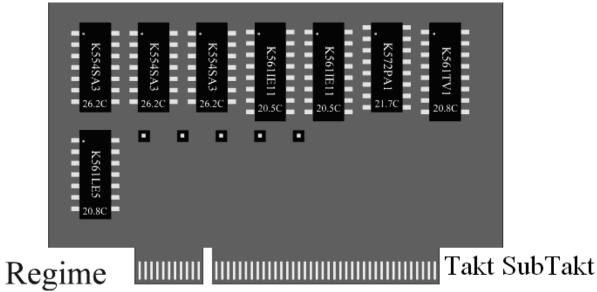

The circuit of the tracking ADC with a reversible counter FP06R [31] is shown in fig. 2.5.

Fig. 2.5. Tracking ADC with reverse counter

Consider an example of optimization of an analog-to-digital serial count converter. The advantage of a serial ADC servo counter with a reversible counter is interference resistance. The presence of even a large noise on the analog input can lead to a longer transition to the equilibrium state, but will not lead to a gross error. The drawback of the tracking ADC is the large time it takes for the feedback signal to change over the entire range. This time can be reduced by dividing the serial counter into sections with the resolution of the section depending on the difference between the input signal (circuit A002 in fig. 2.5) and the feedback signal (circuit A003 in fig. 2.5). The outputs of all counters, as in the main circuit in fig. 2.5, connected to the input of the DAC. Instead of one comparator in the main circuit, a group of comparators is connected, the number of which corresponds to the number of sections of the counter CTR. At the outputs of the comparator, in order to synchronize signal changes and eliminate intermediate states, synchronous triggers are installed in those cases when they are included in the comparator. Comparators must differ in response thresholds, the outputs of the comparators are connected to logic circuits, and the outputs of the latter allow operation of the lower sections of the counter. It is necessary to evaluate the optimal number of CTR sections by the selected criterion. For the criterion of "cost-performance", the optimal structure of the ADC of a sequential count is achieved by dividing the counter into two parts for the senior and lower digits, introducing an additional comparator and logic circuit, and controlling the operation of the counters. in order to synchronize signal changes and exclude intermediate states, synchronous triggers are set in those cases when they are included in the comparator. Comparators must differ in response thresholds, the outputs of the comparators are connected to logic circuits, and the outputs of the latter allow operation of the lower sections of the counter. It is necessary to evaluate the optimal number of CTR sections by the selected criterion. For the criterion of "cost-performance", the optimal structure of the ADC of a sequential count is achieved by dividing the counter into two parts for the senior and lower digits, introducing an additional comparator and logic circuit, and controlling the operation of the counters. in order to synchronize signal changes and exclude intermediate states, synchronous triggers are set in those cases when they are included in the comparator. Comparators must differ in response thresholds, the outputs of the comparators are connected to logic circuits, and the outputs of the latter allow operation of the lower sections of the counter. It is necessary to evaluate the optimal number of CTR sections by the selected criterion. For the criterion of "cost-performance", the optimal structure of the ADC of a sequential count is achieved by dividing the counter into two parts for the senior and lower digits, introducing an additional comparator and logic circuit, and controlling the operation of the counters. the outputs of the comparators are connected to the logic circuits, and the outputs of the latter allow the operation of the lower sections of the counter. It is necessary to evaluate the optimal number of CTR sections by the selected criterion. For the criterion of "cost-performance", the optimal structure of the ADC of a sequential count is achieved by dividing the counter into two parts for the senior and lower digits, introducing an additional comparator and

logic circuit, and controlling the operation of the counters. the outputs of the comparators are connected to the logic circuits, and the outputs of the latter allow the operation of the lower sections of the counter. It is necessary to evaluate the optimal number of CTR sections by the selected criterion. For the criterion of "cost-performance", the optimal structure of the ADC of a sequential count is achieved by dividing the counter into two parts for the senior and lower digits, introducing an additional comparator and logic circuit, and controlling the operation of the counters.

Fig. 2.6. Circuit diagram roughlyprecision ADC fp06rgt

Insignificant hardware costs allow increasing the ADC performance by an order of magnitude [31]. The results are confirmed by an analysis of the values of the effectiveness criterion. The main advantage is roughly accurate ADCs are the ability to set the predicted range of values using the installation inputs of the counter and reducing the input information flow [12]. The output results correspond to the deviation from their predicted values.

The optimization of structures is effective for analog-to-digital devices based on various principles. For example, an ADC of one sample can be built of two ADCs of one sample of a lower bit, a DAC of higher digits, an analog processor that performs the function of subtracting the output voltage of a coarse DAC from the input signal, multiplying the difference by a scale factor, and a digital adder that calculates the sum of the ADC codes of the lower and senior ranks. The input signal is converted by the ADC of higher digits. The high-end ADC output code is converted by the DAC into an analog signal and subtracted by the analog processor (AP) from the input signal. From the AP output, the signal difference multiplied by the scale factor (SF) is converted by the ADC of the lower digits. The output code of the ADC of the upper and lower digits is fed to the digital adder.

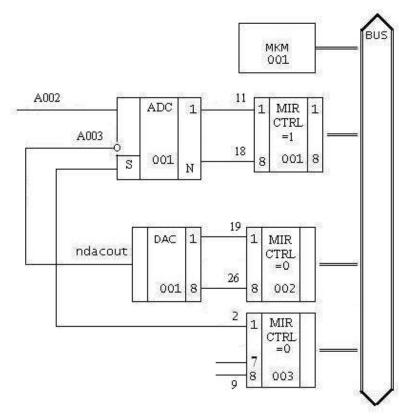

To test the effectiveness of the ADC, the entire working part was removed from the circuit - a rough counter, an accurate counter and the logical structure

that ensures their operation. Instead, a micromachine and two parallel interface registers of the MIR type were introduced: one for receiving information from comparators and transmitting it to the micromachine, and the second for receiving information from the micromachine and transmitting it to the DAC.

The introduction of a micromachine allows both operational processing and the presentation of results to the operator. In addition, it became possible to flexibly change the operational processing algorithm. The formalized task is presented in the fp08padc files [27–29].

The micromachine implements three signal prediction modes: zero mode - emulation of the tracking counter; the first mode - the signal change rate is known in advance; full information mode - the input signal or object model is known.

#### 2.4. Inhomogeneous computing systems based on microEBM

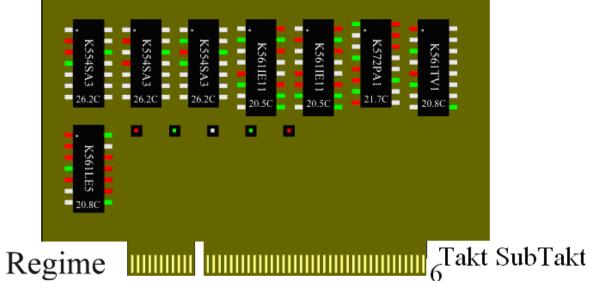

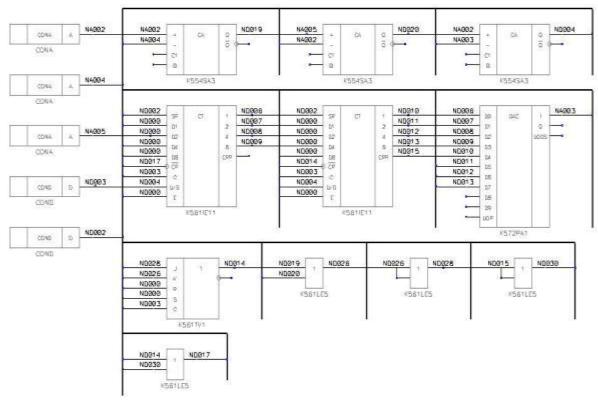

The complexity of the task of the design depends on the indefiniteness of the system structure [29–33, 101–103], components and external influences. As an example, consider the option of a computer system based on microEBM, which are shown in the fig. 2.7–2.14. The systems are designed for the rapid assessment of the parameters of the input signals for several channels and are distinguished by their performance.

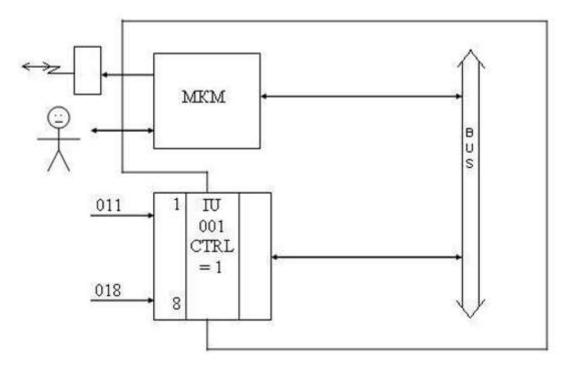

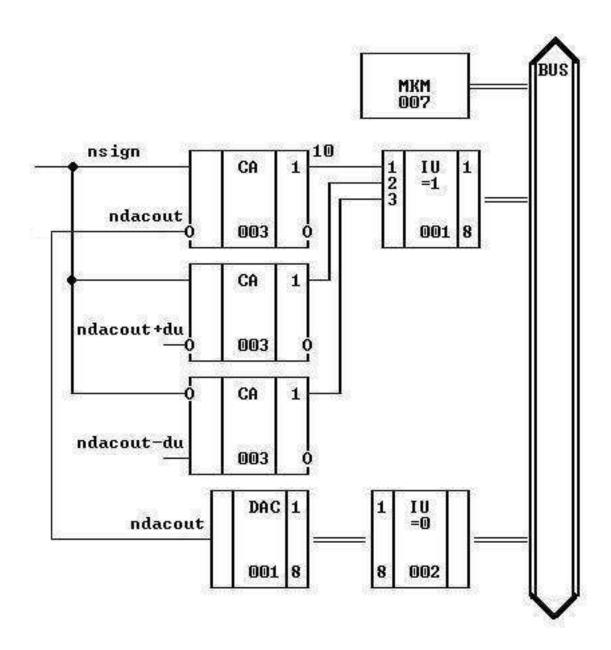

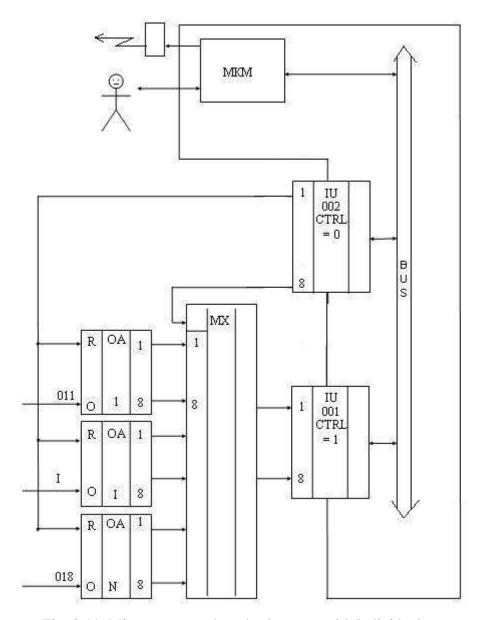

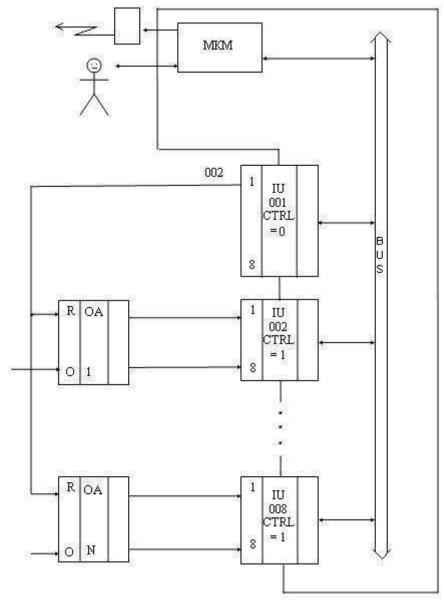

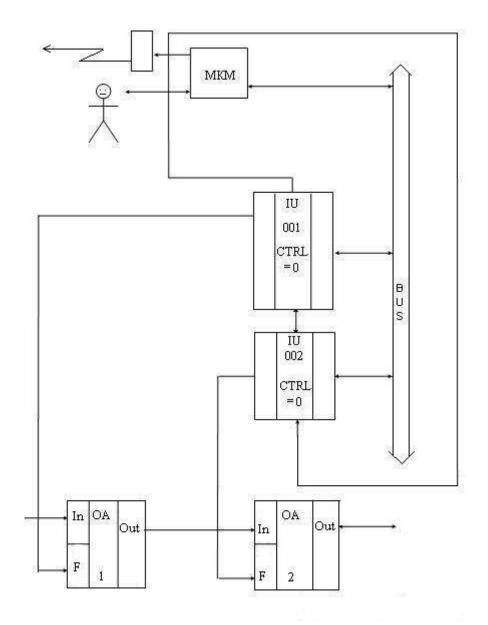

The structure of the system shown in fig. 2.7, consists of microEBM and interface units for input and output of digital signals. Analog signals must first be converted to code. The processing of information is carried out only programmatically, so the productivity of the system will be minimal.

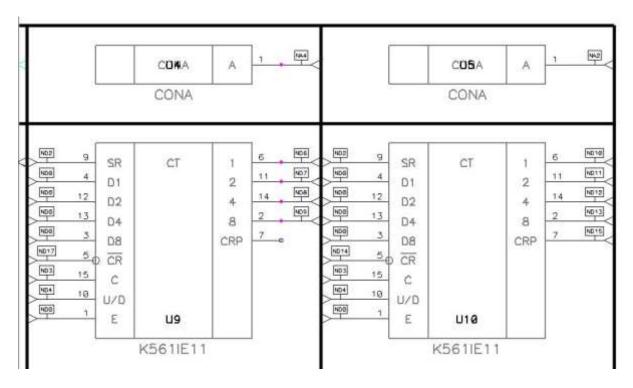

The microcomputer-based subsystem with interval prediction and estimation of signal deviations from the expected one is shown in fig. 2.8. Knowing the number of teams to process one of the words NK and the average duration of the TK command, you can evaluate the productivity of P (1) processing of 31 input words.

Secondly, the structure includes a general control for all channels-controlled operational automatic pre-processing of the input signals. A subsystem based on a microcomputer with interval prediction and estimation of signal deviations over switched channels is shown in fig. 2.10. In order to reduce the number of devices and the cost, the operating circuit breaker was selected as common for all channels. MicroEBM is used immediately for automatic control, for the final processing of the results and the provision of their processing. The control of the automatic is reduced to the transfer to the relevant interface of the controllers of the initial setting for the resolution of the work and the preservation of the food.

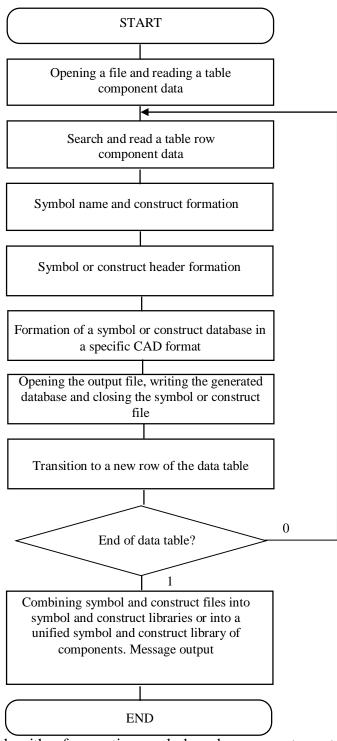

Fig. 2.7. Microcomputer-based subsystem without additional operating nodes